Runzhou Chen

Student at UCLA

University of California, Los Angeles (UCLA)

About

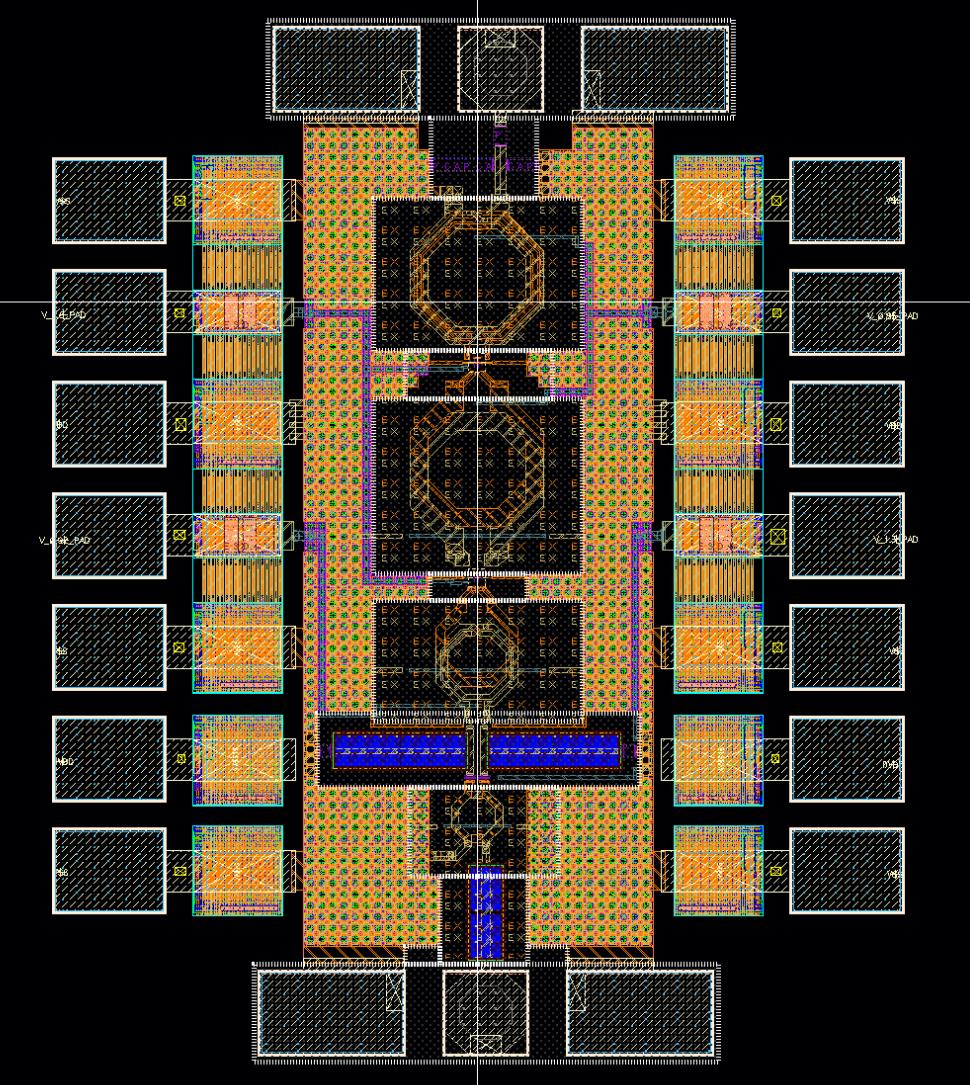

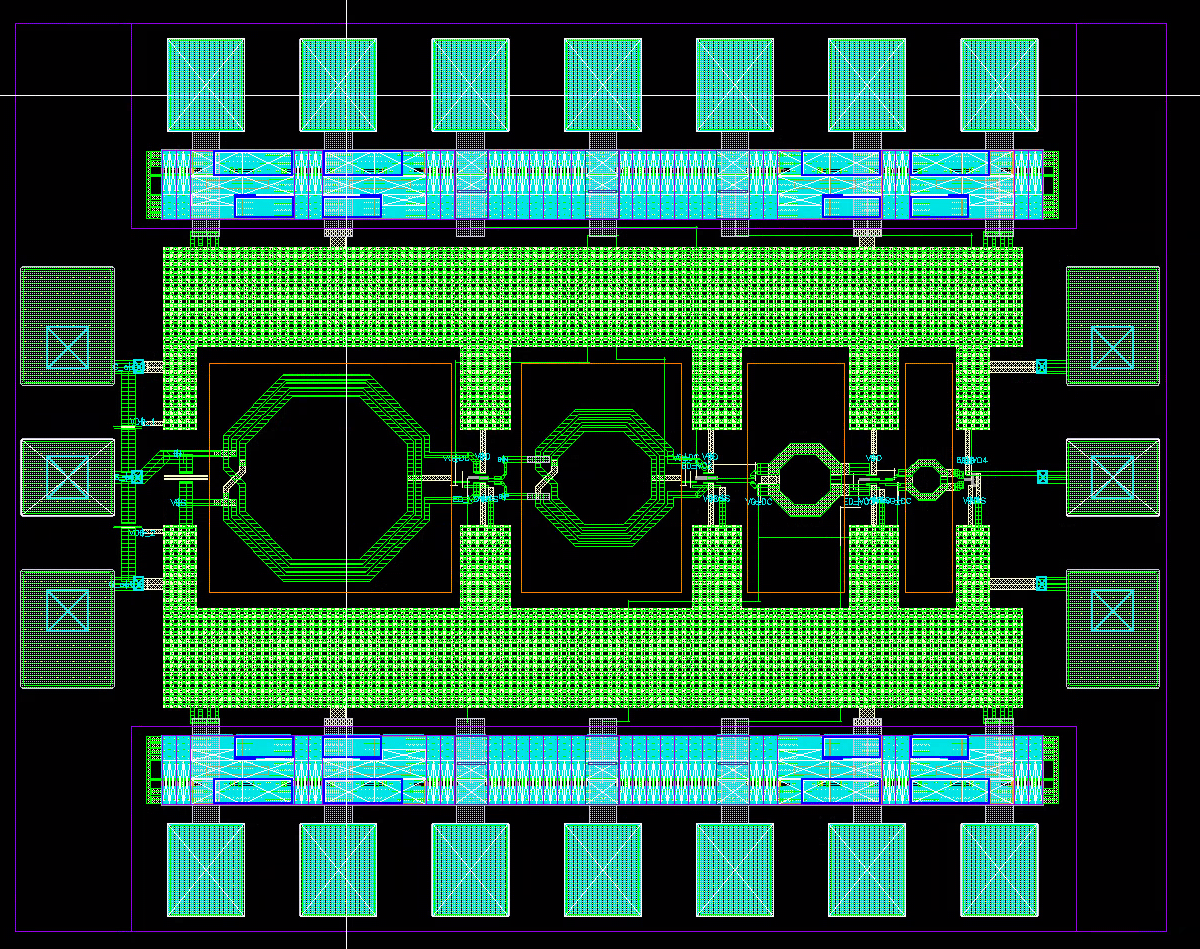

Runzhou Chen received his BEng in Electronic and Computer Engineering from Hong Kong University of Science and Technology (HKUST) with first class honor in July, 2021. His undergraduate research was focused on Visible Light Communication (VLC) and was done in the Optical Wireless Lab (OWL), supervised by Professor Patrick Yue. He joined University of California, Los Angeles (UCLA) in September, 2021 as a master student in Electronic and Computer Engineering. Currently he is doing research at the High Speed Electronics Lab (HSEL), supervised by Professor M. C. Frank Chang.

Runzhou Chen’s research interests include mm-wave and high frequency circuits and systems. He is working on the D-Band FMCW radar with Ph.D. students in HSEL.

Interests

- Mm-Wave and High Frequency Circuits and Systems

- Analog IC Design

- Internet of Things

Education

-

Master of Science in Electronic and Computer Engineering, 2023

University of California, Los Angeles (UCLA)

-

Bachelor of Engineering in Electronic and Computer Engineering, 2021

Hong Kong University of Science and Technology